SKAITMENINĖS LOGIKOS PRADMENYS. LB 4

Detali informacija

Ištrauka

SKAITMENINĖS LOGIKOS PRADMENYS

LABORATORINIO DARBO ATASKAITA

Turinys

1. Įvadas 3

2. Užduotis 4

2.1. Laboratorinio darbo užduotis 4

3. Schemos 4

3.1. Pirmoji schema 4

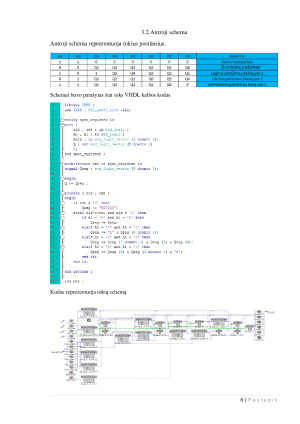

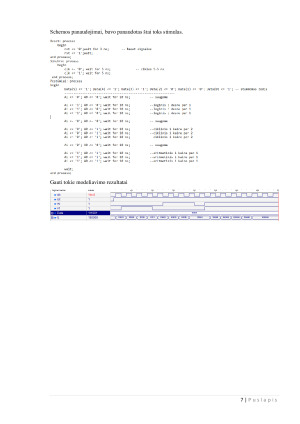

3.2. Antroji schema 6

3.3. Trečioji schema 8

4. Išvados 9

1. Įvadas

Tikslas Susipažinti su aparatūros aprašymo kalbomis ir jų galimybėmis. Aprašyti

kombinacinę ir nuoseklios logikos schemą VHDL kalba, atlikti schemos sintezę ir išanalizuoti sintezės

rezultatus.

Aparatūros aprašymo kalbos Didėjant schemų integracijai ir sudėtingumui, atsiranda

būtinybė greitai ir efektyviai aprašyti aparatines sistemas. Šiuo metu schemų aprašymui naudojamos

trys pagrindinės kalbos: VHDL, Verilog ir SystemC. Šios kalbos turi IEEE standartus bei

projektavimo, modeliavimo ir verifikavimo įrankius. Sukurti komerciniai įrankiai dažnai palaiko

kelias kalbas. VHDL (angl. Very-high-speed integrated circuits Hardware Description Language)

kalba buvo sukurta siekiant sukurti paprastą ir aiškų būdą dokumentuoti schemas. Pagrindinis šios

kalbos privalumas – galimybė aprašyti lygiagrečius procesus ir duomenų srautus. Tuo ji skiriasi nuo

procedūrinių kalbų, tokių kaip C, BASIC ar asembleris, kurios vykdomos nuosekliai, instrukcija po

instrukcijos.

Abstrakcijos lygiai Naudojant sistemų aprašymo kalbas, projektą galima aprašyti

skirtingais būdais. Pagrindinis skirtumas tarp aprašymo būdų yra kaip tiksliai aprašoma fizinė

aparatūra. Šie būdai vadinami abstrakcijos lygmenimis. Kylant abstrakcijos lygiui, aprašas tampa

suprantamesnis žmogui, tačiau sunkiau jį modeliuoti ar transformuoti į fizinį aparatūros aprašą.

Skirtingų sistemų aprašymo kalbų apimami lygmenys šiek tiek skiriasi. Šis skirtumas pavaizduotas 1.1

pav. Ta pati sistema VHDL kalba gali būti aprašyta šiais abstrakcijos lygmenimis

Procesas PROCESS sakinys yra nuoseklus kodas VHDL kalboje. Jį galima pažinti iš IF,

WAIT, CASE bei LOOP sakinių jo viduje, bei jautrumo sąrašo. Processas aprašomas pagrindiniame

kode ir yra įvykdomas kaskart, kai pasikeičia signalas, esantis jautrumo sąraše.

2. Užduotis

2.1. Laboratorinio darbo užduotis

Laboratorinjio darbo užduotis yra parašyti 3 kodus VHDL kalba, kurios sukurti schemas.

Laboratorinio darbo numeris yra 208.

Pirmoji schema yra, kurioje atrinkus tam tikrus skaičius ir padavus skaičių ciklą nuo 0 iki 63,

atsakymas tampa teigiamu kada yra prieinami skaičiai.

Pirmosios schemos skaičiai yra: 0,7,8,15,16,23,24,25,26,27,30,31,48,55,57,58,59,62

Antroji schema yra registras, jame, multiplekserio pagalba, įvykdomas įrašymas bei 3

skirtingi postūmiai.

Mūsų mokslo darbų bazėje yra daugybė įvairių mokslo darbų, todėl tikrai atrasi sau tinkamą!