LAIKMAČIŲ GRUPĖS PROJEKTAVIMAS SU ACTIVE-HDL. Kursinis

Detali informacija

Ištrauka

LAIKMAČIŲ GRUPĖS PROJEKTAVIMAS SU ACTIVE-HDL

KURSINIS DARBAS

TURINYS

TURINYS 2

Įvadas 3

Įrenginio struktūros aprašymas 3

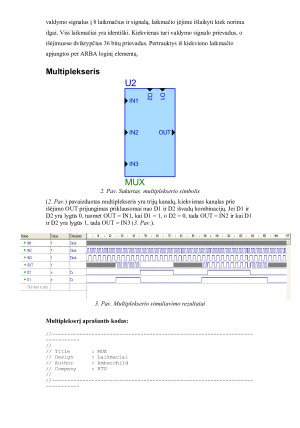

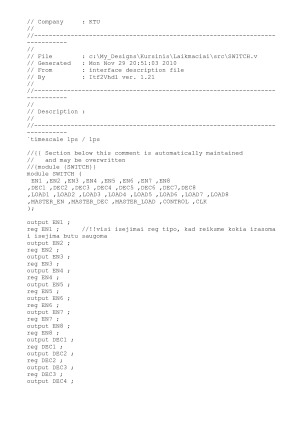

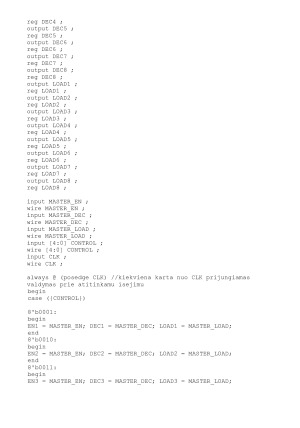

Multiplekseris 4

Preskaleris 6

Multiplekseris + Registras 8

Laikmatis 11

8 ARBA Komponentas 14

Išvados 17

Įvadas

Šiame kursiniame darbe yra atliekamas projektavimas Acitve-HDL aplinkoje.

Pagrindinis darbo tikslas yra suprojektuoti 36 bitų laikmačių grupę, kuri būtų

patogiai valdoma multipleksavimo metodu. Laikmačių grupei priklauso vienas 8 bitų

preskaleris. Prie preskalerio prijungimas taktinis signalas kuris gali būti paduodamas

iš išorinio šaltinio arba iš dviejų vidinių. Šaltinį, kuris bus naudojamas pasirenkame

multiplekserio pagalba. Kiekvienas laikmatis grupėje (jų yra 8) gali būti nustatomas į

inkrementavimo arba dekrementavimo rėžimą. Kiekvienam laikmačiui galima įkrauti

skaičiavimo reikšmę. Taip pat kiekvieną laikmatį galima išjungti/įjungti

individualiai. Papildomai kiekvienas laikmatis turi pertrauktį generuojantį signalą, jis

iššaukiamas kaskart kai laikmatis yra perpildomas.

Įrenginio struktūros aprašymas

1. Pav. Laikmačių grupės blokinė diagrama

(1. Pav.) Pavaizduota įrenginio struktūra. Matome kaip taktinis dažnis parinktas

multiplekserio, yra tiekiamas į preskalerį, kuris pakeisto dažnumo taktinį signalą,

paskirsto į visus laikmačius. Kito multiplekserio + registro uždavinys yra paskirstyti

valdymo signalus į 8 laikmačius ir signalą, laikmačio įėjime išlaikyti kiek norima

ilgai. Visi laikmačiai yra identiški. Kiekvienas turi valdymo signalo prievadus, o

išėjimuose dvikrypčius 36 bitų prievadus. Pertrauktys iš kiekvieno laikmačio

apjungtos per ARBA loginį elementą.

Mūsų mokslo darbų bazėje yra daugybė įvairių mokslo darbų, todėl tikrai atrasi sau tinkamą!